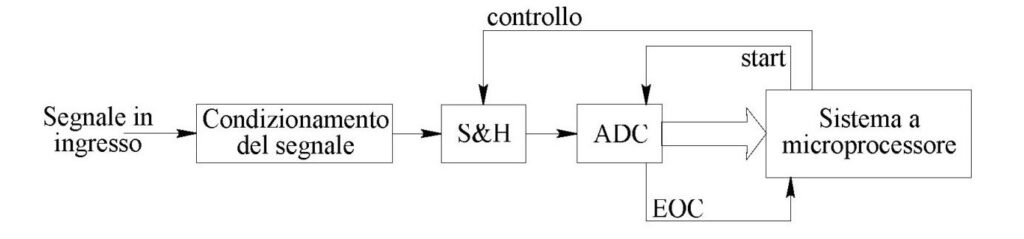

Per elaborazione dei dati si intende una qualsiasi manipolazione di un segnale di ingresso generato da un trasduttore da parte di un generico elaboratore allo scopo di rendere utile il dato acquisito.

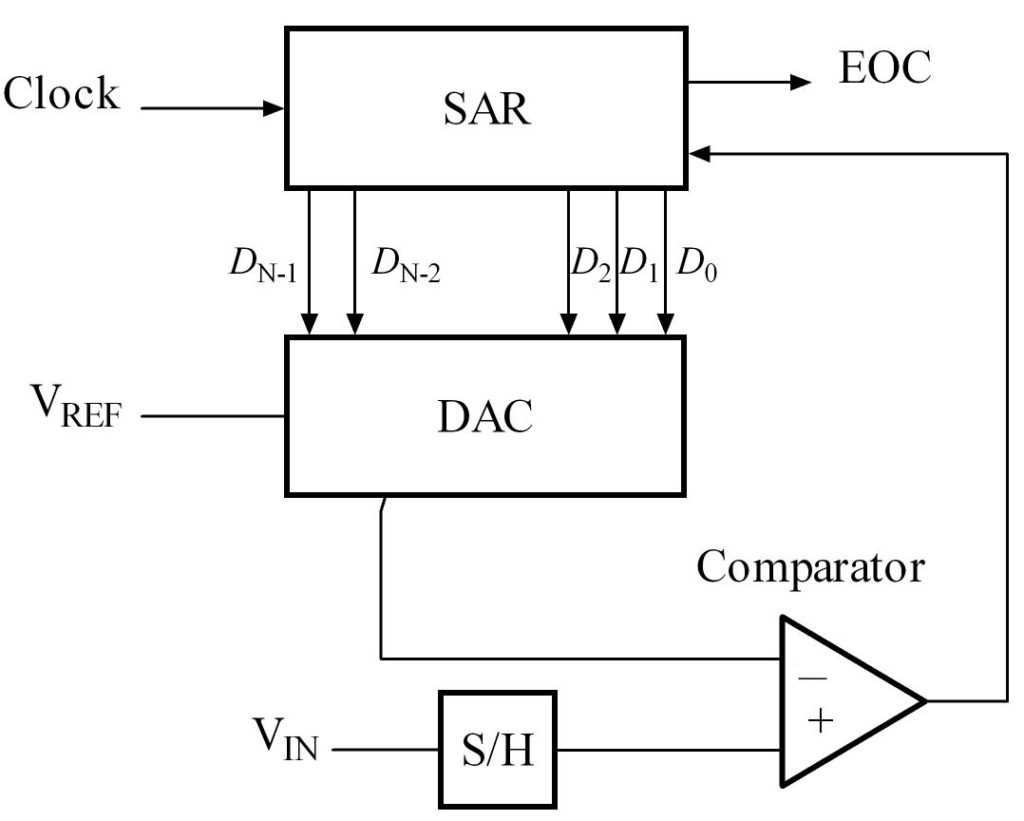

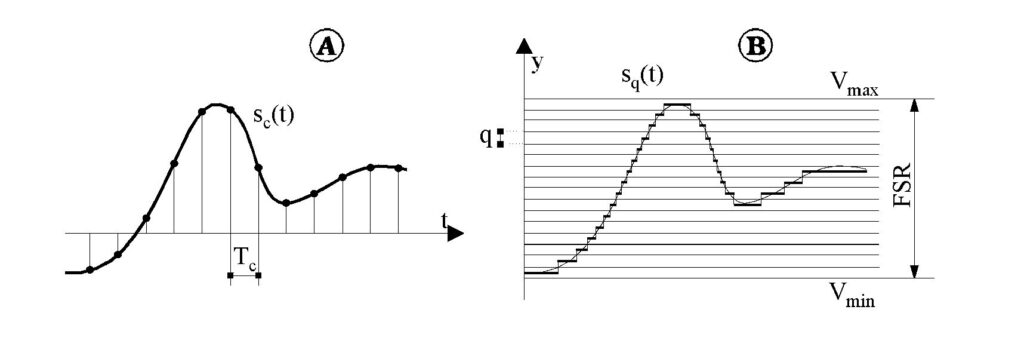

Siccome l’uscita del trasduttore è di tipo analogica per essere manipolata ed elaborata dal PIC deve essere convertita in digitale. Pertanto, i segnali analogici, vengono trattati da convertitori analogico-digitali (ADC) i quali fornisco in uscita stringhe di bit che rappresentano numeri proporzionali ai valori del segnale di ingresso. Il processo di digitalizzazione dei segnali analogici introduce il concetto di quantizzazione. Infatti mentre un segnale analogico può assumere infiniti valori in un campo continuo, la sua rappresentazione digitale può assumere soltanto un numero finito di valori discreti. Gli infiniti valori del segnale analogico devono pertanto essere quantizzati ovvero raggruppati in un certo numero di fasce delimitate da livelli fissi detti livelli di quantizzazione Q; a ciascuna fascia di valori analogici corrisponderà un valore digitale. La distanza fra due livelli di quantizzazione contigui costituisce il passo di quantizzazione Q, a cui corrisponde il valore del bit meno significativo (LSB). Un dato digitale ad n bit può assumere 2n valori; il valore digitale 2n viene pertanto associato al valore di fondo scala (FS) della grandezza analogica. Conseguentemente il valore analogico corrispondente al bit meno significativo sarà . Inoltre si dimostra che l’errore di quantizzazione che viene commesso è sempre minore o uguale a ½ LSB. In un ADC i valori digitali di uscita non riproducono dunque fedelmente il segnale di ingresso ma ne danno una rappresentazione approssimata, tanto più precisa quanto minore è il passo di quantizzazione Q, cioè quanto più numerosi sono i livelli quantizzazione. Questi ultimi, d’altra parte, sono legati al numero di bit utilizzati per la rappresentazione digitale e quindi sono necessariamente in numero limitato. Sono comuni convertitori A/D con uscite a 8, 10, 12 bit, che consentono, rispettivamente, 28 = 256, 210 = 1024, 212 = 4096 livelli di quantizzazione. Il numero di bit di uscita di un convertitore A/D viene generalmente chiamato risoluzione poiché implicitamente indica qual è la minima variazione del segnale di ingresso che può essere rivelata in uscita. Un altro concetto implicito nella conversione A/D è quello di campionamento del segnale in vari istanti successivi. Infatti la conversione consiste nel prelevamento di un campione del segnale ad un dato istante e nella determinazione del corrispondente valore digitale, che resterà fisso finché non verrà prelevato un nuovo campione per una nuova conversione. La frequenza con cui il segnale viene prelevato è detta frequenza di campionamento ed ha un’importanza fondamentale in riferimento al contenuto informativo del segnale e alle possibilità di ricostruire fedelmente il segnale analogico originario. Il teorema di campionamento, noto anche come teorema diShannon, stabilisce che la frequenza di campionamento deve essere maggiore o uguale al doppio di quella della componente di frequenza più elevata del segnale in esame e la banda del segnale deve essere limitata. Pertanto un segnale analogico la cui componente armonica più elevata abbia frequenza $f_{max}$, potrà essere ricostruito fedelmente dai valori campionati se la frequenza di campionamento è:

$$f_{c}\geq f_{max}$$

Campionamento (A) e quantizzazione (B) di un segnale analogico

Dal momento che i convertitori A/D impiegano un tempo tconv finito (approssimativamente da 20ms a 1ns con ADC ad alta velocità) per digitalizzare un segnale analogico in ingresso, eventuali variazioni del segnale durante il processo di conversione possono determinare errori significativi. Per tale motivo il campionamento di un segnale può essere effettuato utilizzando circuiti di campionamento e tenuta (S/H: sample and hold) in grado di compiere un campionamento “veloce” del segnale analogico e di mantenere stabile il valore acquisito durante tutto il processo di conversione.

ADC PIC16F887

Il PIC16F887 dispone di 14 ingressi analogici, e mediante opportuni selettori, configurabili internamente è possibile selezionare il segnale d’ingresso che verrà sottoposto al processo di conversione. Il convertitore A/D interno ha una risoluzione di 10 bit ad approssimazioni successive, che permette di avere 1024 livelli. Il valore di questi livelli viene salvata nei due registri dell’ADC ADRESL e ADRESH. Altri due registri fondamentali che troviamo sono ADCON0 e ADCON1 che rispettivamente sono utilizzati per la frequenza di conversione, le tensioni di riferimento, l’accensione/spegnimento, la selezione dell’ingresso dal quale prelevare il segnale, l’avvio delle operazioni di conversione ecc. Per il settaggio delle porte, da digitale ad analogico, avviene invece tramite due registri che sono ANSEL e ANSELH. La maggior parte dei progetti assumono la VDD come valore di riferimento, talvolta, però tale valore è eccessivo quando i valori di tensione da analizzare sono troppo piccoli ovvero quando una maggior precisione sia determinante. Per ottenere un valore di VREF+ più piccolo utilizzeremo un trimmer portando la tensione di riferimento a 2,5V. Se la VREF+ è stata settata a 2.5V si calcola il passo di quantizzazione = 2500/1024 = 2,441 mV. Se avremo lasciato VREF+ = 5V avremo avuto un quanto di 4,881mV (meno preciso).